...When They Attack In Packs

"Polygons feel no pain" Volume 3

Ingemar Ragnemalm

Course book in GPU computing

# Foreword

In the past, I wrote "Polygons feel no pain" and "so how can you make them scream?". For several years I have considered making a small course book for my part of TDDD56 "Multicore and GPU programming" so you have something that firmly summarizes my part of the course, complete and without too much fluff.

There are other books on the topic, of course, and some are pretty neat and non-bulky. However, they are usually focused entirely on CUDA, possibly with some OpenCL material but hardly more. This book, although brief, has the ambition to give an introduction to the field with a wider scope, including several other platforms of interest.

I may not be a known expert in the field, but having worked with this concept since 2005, giving my first GPU computing course before CUDA even existed, I feel that I should be capable of providing a decent book.

Parts of the book are based on the GPU computing chapter of Volume 2. Much of the contents is also based on NVidia's CUDA programming guide. [3] Another important source is Mark Harris' blog entries, e.g. [15]

You should immediately see that the name fits with the names of the earlier books. It also refers to a rarely heard joke that I remember, I think it was from a crowded university party:

"Ingen panik! Anfall i flock! Alla på en gång!"

which translates to

"No panic! Attack in packs! Everybody at the same time!"

For some reason I never forgot that and it fits right in.

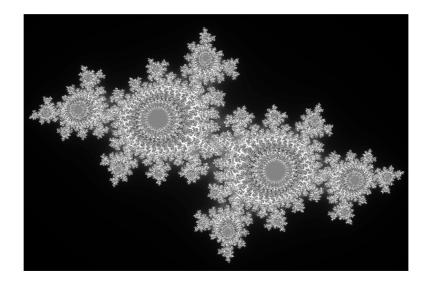

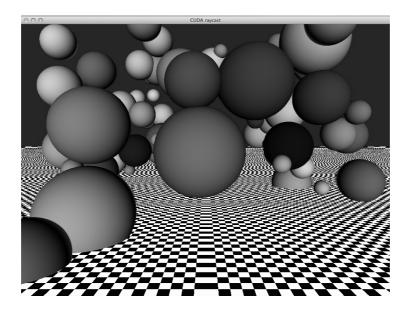

Cover image by myself, "a pack of 'cudas".

Related web page: http://www.computer-graphics.se

All content of the book is © Ingemar Ragnemalm 2018 except for cited material as documented.

ISBN 978-91-7773-719-3

First edition 2018.

# 1. Introduction

This book was written as course material for the latter part of the course in "TDDD56 Multcore and GPU programming".

# 1.1 Who should read this book?

Since this book is written for part of the course TDDD56 at the University of Linköping, attendants of that course are the target audience. It is also likely to be used in PhD courses on the GPU Computing concept. Anyone else interested in the subject is also in the target audience!

The purpose of the book is to provide a broad overview of the GPU Computing programming subject, far broader than most other books.

### 1.2 What should you expect to learn from this book, and its course?

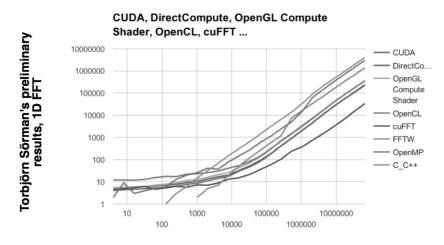

This book spends most of its pages on CUDA, but it is not a CUDA book. Rather, it has an unusually broad scope, covering most GPU computing technologies of interest.

- 1. GPU history and architecture.

- 2. CUDA

- 3. OpenCL

- 4. Compute Shaders

- 5. Fragment shaders

- 6. Specific problem areas.

We start with CUDA for the simple reason that it is the API that is by far easiest to get started with. Once you know it, however, you will find it pretty easy to move to any of the others.

Most code examples will be in CUDA, but the book will aim towards covering the other platforms as well, with emphasis on OpenCL and OpenGL Compute Shaders. We can not

put all code examples for all platforms in the book, but there will be a (slowly) growing amount of accompanying code on my website, computer-graphics.se.

Thus, let us emphasize this: This is not a CUDA book, this book is not only about CUDA. It is a general GPU Computing book, although mostly using CUDA for examples for space and readability reasons, but I strongly advocate diversity and being knowledgeable of alternatives. And there are some strong ones to consider.

# **1.3 Acknowledgments**

The material for this book comes from a variety of sources, books, papers, web pages.

The first contributor was Erik Pettersson [2]. In 2005, he made an early GPU Computing project as master thesis, with me as examiner. Later, Johan Hedborg, Fredrik Viksten and Jens Ogniewski have contributed, first to my PhD courses and later to the TDDD56 course. Finally, the collaboration with Christoph Kessler and his group over the course has been most important and fruitful. The recent (2017) move towards more image processing in the course was particularly nice for me, since I have a background in image processing, and has influenced chapter 18.

Finally, all previous students on the courses have contributed in various ways. Your interest for certain problems have been very important for the course.

At the top-right in this pile is an NVidia 8500 GT, my first CUDA capable GPU, and on top-left (that is left in the picture) is an ATI Radeon 9800 PRO, the card on which I made my first GPGPU experiments.

# 2. Table of contents

| 1. | Introduction                                                                                              |                                                                        |    |  |  |

|----|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----|--|--|

|    | 1.1                                                                                                       | Who should read this book?                                             |    |  |  |

|    | 1.2                                                                                                       | What should you expect to learn from this book, and its course?        |    |  |  |

|    | 1.3                                                                                                       | Acknowledgments                                                        |    |  |  |

| 2. | Tabl                                                                                                      | e of contents                                                          |    |  |  |

| 3. | How                                                                                                       | How did we get here?                                                   |    |  |  |

|    | 3.1                                                                                                       | Related efforts                                                        |    |  |  |

|    | 3.2                                                                                                       | Why did GPUs get so much performance?                                  |    |  |  |

|    | <ul><li>3.3 The arrival of GPU computing: General Purpose computation on Graphics F<br/>Units14</li></ul> |                                                                        |    |  |  |

|    |                                                                                                           | 3.3.1 Key components of the GPGPU trend                                |    |  |  |

|    |                                                                                                           | 3.3.2 GPGPU/GPU computing approaches                                   |    |  |  |

|    |                                                                                                           | 3.3.3 Fixed pipeline GPGPU                                             |    |  |  |

|    |                                                                                                           | <ul><li>3.3.4 Fragment shader based GPGPU</li><li>3.3.5 CUDA</li></ul> |    |  |  |

|    |                                                                                                           | 3.3.6 OpenCL                                                           |    |  |  |

|    |                                                                                                           | 3.3.7 OpenGL Compute shaders                                           |    |  |  |

|    |                                                                                                           | 3.3.8 Direct Compute                                                   |    |  |  |

|    |                                                                                                           | 3.3.9 Vulkan                                                           |    |  |  |

|    | 3.4                                                                                                       | Applications                                                           |    |  |  |

|    |                                                                                                           | 3.4.1 Image processing, image analysis and video coding                |    |  |  |

|    |                                                                                                           | 3.4.2 Crypto currency mining                                           |    |  |  |

|    |                                                                                                           | 3.4.3 Deep learning                                                    |    |  |  |

| 4. | GPU                                                                                                       | J architecture                                                         | 19 |  |  |

|    | 4.1                                                                                                       | SIMD and SIMT                                                          |    |  |  |

|    | 4.2                                                                                                       | SIMT, Single Instruction, Multiple Thread                              |    |  |  |

|    | 4.3                                                                                                       | The unified architecture                                               |    |  |  |

|    | 4.4                                                                                                       | SMs, SPs and shared memory                                             |    |  |  |

| 5. | Hello World!                                                                                              |                                                                        |    |  |  |

|    | 5.1                                                                                                       | Hello CUDA                                                             |    |  |  |

|    | 5.2                                                                                                       | Hello OpenCL                                                           |    |  |  |

|    | 5.3                                                                                                       | Hello GPGPU                                                            |    |  |  |

|    | 5.4                                                                                                       | Hello Compute Shaders                                                  |    |  |  |

|    |                                                                                                           | 5.4.1 Main program                                                     |    |  |  |

|    |                                                                                                           |                                                                        |    |  |  |

|    |      | 5.4.2 Kernel                                 | 33 |

|----|------|----------------------------------------------|----|

|    | 5.5  | Direct Compute and Vulkan                    | 34 |

| 6. | CUDA | A                                            | 35 |

|    | 6.1  | Simple CUDA example                          | 36 |

|    | 6.2  | Modifiers for code                           | 36 |

|    | 6.3  | Memory management                            | 37 |

|    | 6.4  | Kernel execution                             |    |

|    | 6.5  | Compiling Cuda                               | 38 |

|    |      | 6.5.1 Compiling CUDA for larger applications |    |

|    |      | 6.5.2 Example of multi-unit compilation      | 39 |

|    |      | 6.5.3 Compiling for MacOSX                   | 40 |

|    | 6.6  | Executing a Cuda program                     | 40 |

|    | 6.7  | Computing with CUDA                          | 40 |

|    | 6.8  | Warps                                        | 40 |

|    | 6.9  | Kernel                                       | 41 |

|    | 6.10 | Grid, blocks and threads                     | 41 |

|    | 6.11 | Indexing data with thread/block IDs          | 41 |

|    | 6.12 | Julia example                                | 42 |

| 7. | Memo | bry access                                   | 45 |

|    | 7.1  | Global memory                                |    |

|    | 7.2  | Shared memory                                |    |

|    | 7.3  | Example: Matrix multiplication               |    |

|    |      | 7.3.1 Matrix multiplication on CPU           |    |

|    |      | 7.3.2 Naive GPU version                      |    |

|    |      | 7.3.3 Optimized GPU version                  | 48 |

|    | 7.4  | Modified computing model                     | 50 |

| 8. | More | language features                            | 51 |

|    | 8.1  | Synchronization                              | 51 |

|    |      | 8.1.1 Global synchronization                 | 52 |

|    | 8.2  | Error checking                               | 52 |

|    | 8.3  | Query devices                                | 53 |

|    | 8.4  | Compute capability                           | 54 |

|    | 8.5  | Timing and profiling                         | 55 |

|    |      | 8.5.1 CPU timers                             | 55 |

|    |      | 8.5.2 CUDA Events                            |    |

|    | 8.6  | CUDA streams and overlapping data transfers  |    |

|    |      | 8.6.1 Multiple streams                       | 57 |

| 9. | Memo | bry access part 2                            | 59 |

|    | 9.1  | Coalescing                                   |    |

|    |      | 9.1.1 Matrix transpose example               | 60 |

|    | 9.2  | Optimizing shared memory                     |    |

|    | 9.3  | Atomic functions                             |    |

|    | 9.4  | Constant memory                              |    |

|    |      | 9.4.1 Ray-caster example                     |    |

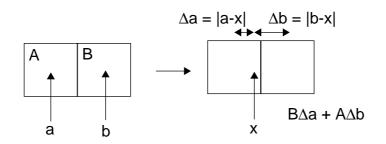

|    | 9.5  | Texture memory/ Texture units                |    |

|    |      | 9.5.1 Texture memory for graphics            |    |

|    |      | 9.5.2 Using texture memory in CUDA           |    |

|    |      | 9.5.3 Clamp and repeat                       | 13 |

|     |        | 9.5.4 Interpolation                          | 73  |

|-----|--------|----------------------------------------------|-----|

|     | 9.6    | Managed/unified memory                       | 74  |

| 10. | Open   | CL                                           | 77  |

|     | 10.1   | OpenCL for GPU Computing                     |     |

|     | 10.2   | OpenCL vs. CUDA terminology                  |     |

|     | 10.3   | OpenCL memory and thread model               |     |

|     | 10.4   | Heterogeneous                                |     |

|     | 10.5   | Language                                     |     |

|     | 10.6   | Walk through the Hello CL example code       | 80  |

|     | 10.7   | The Julia example in OpenCL                  |     |

|     | 10.8   | Some more notes on OpenCL                    | 84  |

|     | 10.9   | Synchronization in OpenCL                    | 84  |

|     | 10.10  | Queries in OpenCL                            | 85  |

|     | 10.11  | OpenCL events                                | 85  |

|     | 10.12  | Conclusions on OpenCL                        | 85  |

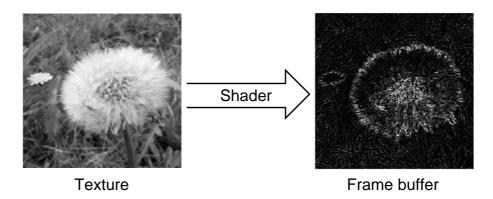

| 11. | Fragn  | nent shaders                                 |     |

|     | 11.1   | Input and output                             |     |

|     | 11.2   | The computation kernel = the shader          |     |

|     | 11.3   | Feedback                                     |     |

|     | 11.4   | Image filter in fragment shader              |     |

|     | 11.5   | Reduction in fragment shaders                |     |

| 12. | Open   | GL Compute shaders and Vulkan                | 93  |

|     | 12.1   | OpenGL Compute shaders                       |     |

|     | 12.2   | Shader Storage Buffer Objects                |     |

|     | 12.3   | Example code                                 |     |

|     | 12.4   | Synchronization in OpenGL compute shaders    |     |

|     | 12.5   | Compute shader timing with query objects     |     |

|     | 12.6   | Queries in compute shaders                   |     |

|     | 12.7   | Conclusions on Compute Shaders               |     |

|     | 12.8   | Vulkan                                       |     |

| 13. | Direc  | t Compute                                    | 99  |

| 101 |        | Shared memory                                |     |

|     | 13.1   | Synchronization                              |     |

| 14. |        | -                                            |     |

|     | -      | Comparisons of the platforms                 |     |

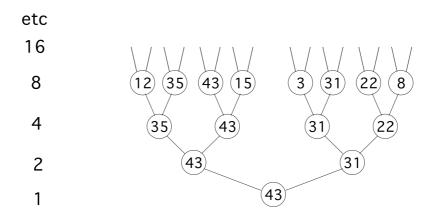

| 15. | Redu   | ction                                        |     |

|     | 15.1   | Optimization of reduction                    |     |

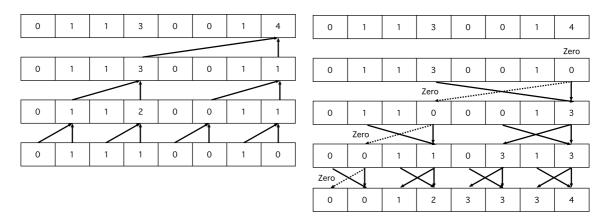

|     | 15.2   | Parallel prefix sum on GPU                   |     |

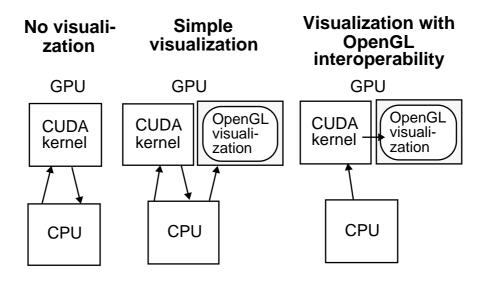

| 16. | Open   | GL Interoperability                          | 109 |

|     | 16.1   | CUDA-OpenGL Interoperability                 |     |

|     | 16.2   | OpenCL and OpenGL                            |     |

|     | 16.3   | OpenGL, Compute Shaders and fragment shaders |     |

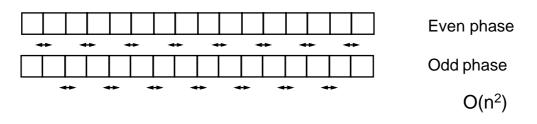

| 17. | Sortir | ng on GPUs                                   |     |

| 17. | 17.1   | Bubble sort                                  |     |

|     | 17.1   | Rank sort                                    |     |

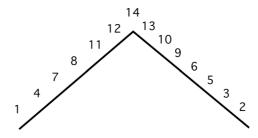

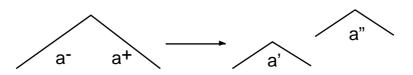

|     | 17.2   | Bitonic sort                                 |     |

|     |        |                                              |     |

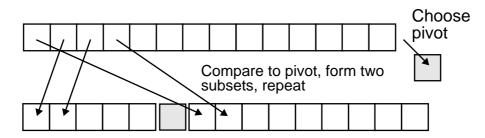

|     | 17.4       | QuickSort                                                                     |

|-----|------------|-------------------------------------------------------------------------------|

|     |            | 17.4.1 Pivot selection                                                        |

|     |            | 17.4.2 Comparisons                                                            |

|     |            | 17.4.3 Partitioning                                                           |

|     |            | 17.4.4 Concatenate result                                                     |

|     | 17.5       | Recursion, Concurrent kernels, Dynamic Parallelism                            |

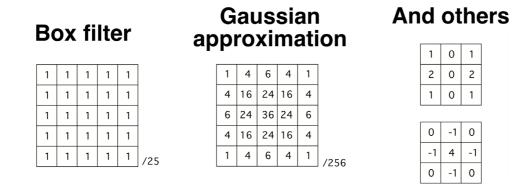

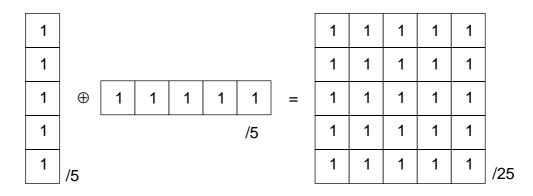

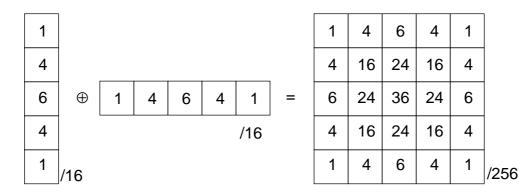

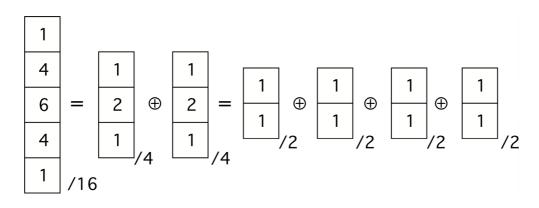

| 18. | Image      | filters                                                                       |

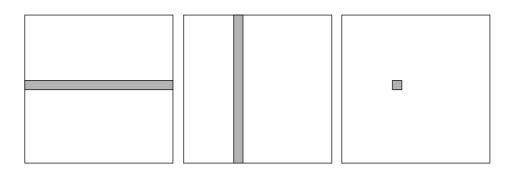

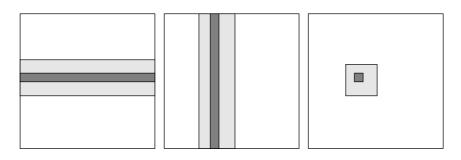

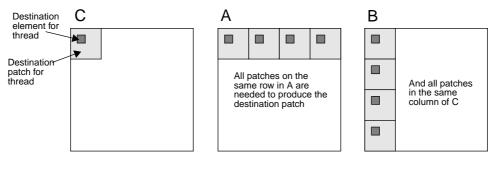

|     | 18.1       | Separable filters                                                             |

|     | 18.2       | Non-linear filters                                                            |

|     | 18.3       | Edge checks, clamping                                                         |

|     | 18.4       | Color images                                                                  |

|     | 18.5       | Scatter vs gather                                                             |

| 19. | Questions1 |                                                                               |

|     | 19.1       | Lecture questions                                                             |

|     |            | 19.1.1 Lecture 1                                                              |

|     |            | 19.1.2 Lecture 2                                                              |

|     |            | 19.1.3 Lecture 3                                                              |

|     |            | 19.1.4 Lecture 4                                                              |

|     |            | 19.1.5 Lecture 5                                                              |

|     | 19.2       | GPU Algorithms and Coding (GPU Algorithms)                                    |

|     | 19.3       | GPU Conceptual Questions (AKA GPU Architecture concepts or GPU Computing) 133 |

|     | 19.4       | GPU Quickies                                                                  |

| 20. | Final v    | words                                                                         |

| 21. | Refere     | nces                                                                          |

| 22. | Index      |                                                                               |

# 3. How did we get here?

Let us start with having a look at how we got here, what developments that led us to the hardware that we have today. This is more than just a peek back in history, it may also give some insights in what to expect from the GPU hardware.

Since personal computers arrived, the development of CPUs can be summarized as follows:

80's: CPU and the memory bus had the same speed, the same clock frequency. The concept "Zero wait states" was an honor word, the CPU never had to wait for the bus more than one clock cycle.

1993: About this time, the 1-1 mapping between CPU and the system was scrapped, instead the term "clock doubling" described the new way; The CPUs was faster than the rest of the system, by 2 or 3 times. This gave us a rapid raise of CPU frequency, making it possible to do more computations between every memory access.

Late 90's to present: We saw multi-CPU systems in the late 90's, but they were initially a limited success. Since then the operating systems have been adapted to fully support multiple CPUs, and we got multi-core CPUs with two cores on a chip. Today, 8 cores is getting increasingly common while 16 cores is available but expensive. Even embedded systems like phones are multi-core, and systems with less than 2 cores are getting rare.

CPUs are still improving, but going for higher frequency is not as obvious as before.

During this time, graphics hardware has undergone an even faster evolution.

80's: Graphics hardware in these days mainly referred to hardware that read pixels from VRAM and put them on a screen. The fanciest hardware acceleration was probably hardware sprites. Graphics programming was very focused on writing pixels to VRAM with low-level code, optimized assembly code.

1993: With the clock doubled/tripled CPUs we got enough power to produce textured 3D games like Wolfenstein 3D and Doom. In a glorious 320x240 resolution, these games were sensations! However, rendering was still a job for the CPU.

But were there not any GPUs? Yes, there was, but they were professional 3D boards, insanely expensive from a home computing point of view. This all changed 1996:

1996: With the 3dfx Voodoo1 board, we suddenly got a GPU that anyone could buy! It was priced pretty much like today's mid-range boards. Of course it did extremely little from a modern point of view, and had a strange solution for switching between 2D and 3D graphics, with a special cable over to the 2D board, but it took gaming from a blocky 320x240 resolution to a slick-looking 640x480.

2001: This year gave us a revolution that was bigger than most people understood: Programmable shaders. For the first time, we could put our own program code into the GPU!

2006: The G80 gave us the "unified architecture", which was much more suited for GPU computing than the older architectures, and with that followed NVidia's CUDA.

2009: The non-NVidia part of the world struck back with OpenCL.

2010: The Fermi architecture was the first GPU architecture that was clearly aimed at GPU computing. It was no success, it made NVidia fall behind in gaming performance, but it was still a milestone, showing what was to come.

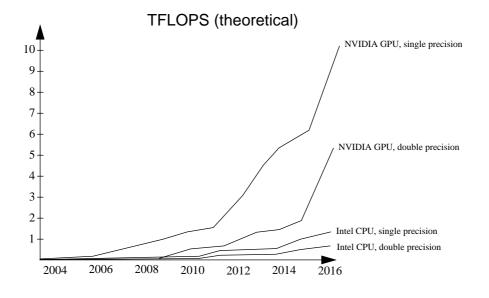

During this process, the number crunching performance of GPUs has increased extremely fast. NVidia tends to show off with graphics like Figure 1.

These graphs look impressive and we get the impression that GPUs are improving at a rate that is way over what CPUs can perform, accelerating away leaving CPUs standing still at the starting line. However, the picture is somewhat misleading. Note that the graphs are always with *linear* scales. If you would make them with logarithmic scale for perfor-

mance, it would look much more like what it is; GPUs and CPUs are both improving at similar rates. GPUs are faster, but the proportions are not changing so much.

But is this a fair comparison? Let us compare apples with apples:

GFLOPS for both!

If we take this in numbers, we get a table like this:

GPU

CPU

1995:

0.001

0.09

2005:

40

5.6

2011:

2488

91

2015:

7000

176

2016:

16380

400-700\*

2017:

110000\*\*

4000\*\*\*

\* Theoretical, 16 cores

\*\*\* Claimed by NVidia on Titan V [5]

\*\*\* Theoretical peak performance [6]

(Other data from various sources, not documented.)

The 2017 part of the table reflects late 2017/early 2018.

CPUs can not compete in peak performance. Even after the biggest steps of progress, they are far behind. On the other hand, remember that this is for the most optimal problems. The advantage of GPUs drop significantly on problems that are less suited for the architecture.

Let us also consider economy. How much does a GFLOPS cost?

```

1961:8.3 trillion1984:42 million1997:42000 (CPU cluster)2000:836-13002007:522012:0.73 (AMD 7970)2013:0.22 (PS4)2015:0.08 (Radeon R9 295)(Source: Wikipedia)

```

That is a price/performance improvement of 104 trillion times since 1961, and only since 2000 computing has become 16000 times cheaper! And that is in an era where CPU clock frequency has stalled, and thus many people may believe that performance doesn't improve! If so, they are just 16000 times wrong (and that is not even counting the improvement since 2015).

# 3.1 Related efforts

So, NVidia and AMD have been the two big ones in graphics and gaming, and had considerable success in general purpose computing. We also have Intel making GPUs integrated in CPUs. They, however, tend to be of little interest for high performance applications.

The GPUs are, of course, mostly compared to the main cores of CPUs. It should be noted that they are less often compared to the processing power of CPUs while using the vector processing units in the CPUs. But there have also been other parallel architectures. At this time, many of them are counted out. IMB had the Cell processor, which even made it into Sony Playstation 3 as well as Namco Bandai arcade boards, but in 2009, its next generation was cancelled, signalling its decline. Intel made the Larabee, which was cancelled in 2010.

However, a successor of Larabee, the *Xeon Phi*, is actively developed, competing with NVidia and AMD for the growing GPU computing market.

The following two tables come from an investigation on the performance on the Phi compared to a CPU, using vector processing extensions, and a high performance GPU. Alas, I have lost the source and am unable to find it. If anyone involved in it reads this, please enlighten me.

|                 | Xeon E5-2670 | <u>Xeon Phi 5110P</u> | <u>Tesla K20X</u> |

|-----------------|--------------|-----------------------|-------------------|

| Cores           | 8            | 60                    | 14 SMX            |

| Logical cores   | 16 (HT)      | 240 (HT)              | 2688 CUDA cores   |

| Frequency       | 2.60 GHz     | 1.053 GHz             | 735 MHz           |

| GFLOPS (double) | 333          | 1010                  | 1317              |

| SIMD width      | 256 bits     | 512 bits              | N/A               |

| Memory          | ≈16-128 GB   | 8GB                   | 6GB               |

| Memory BW       | 51.2 GB/s    | 320 GB/s              | 250 GB/s          |

| Threading       | software     | software              | hardware          |

So, how does it complete? The same investigation (I *think* it was) also gave us benchmarks, with the following table:

| Paths | <u>Sequential</u> | Sandy-Bridge CPU* | <u>Xeon Phi*</u> | <u>Tesla GPU</u> |

|-------|-------------------|-------------------|------------------|------------------|

| 128K  | 13.062 s          | 694 ms            | 603 ms           | 146 ms           |

| 256K  | 26.106 s          | 1.399 s           | 795 ms           | 280 ms           |

| 512K  | 52.223 s          | 2.771 s           | 1.200 s          | 543 ms           |

\* using SIMD vector intrinsics

My conclusion of this particular investigation is that the GPU still wins, even by a considerable margin, but the Phi, and even a CPU using vector extensions, are still fighting to give it a run for the money.

Note how much faster the CPU was by using the often ignored vector intrinsics. A 20 times speedup, for something that we always have available! But all these except the poorly performing sequential CPU solution require you to code in parallel! So whatever you do, if you want to compete in performance, you must learn parallel programming, you must *attack in packs*!

And that is why you are here, right?

# 3.2 Why did GPUs get so much performance?

So, the GPU is pretty fast. Let me now argue for why the GPU got all that power in the first place.

There have been many earlier attempts to construct parallel computers. However, generally speaking, they have all failed to be mass market product due to lack of a big problem suited for parallel implementation with wide enough user base to get the volumes up.

This problem was provided by the gaming industry, by the demand for good graphics. This makes it an early problem with large amounts of data, with its complex geometry and millions of output pixels. It could, with great benefits, be accelerated. The graphics pipeline is designed with excellent opportunities for parallelism!

So, we got a volume product! The 3D graphics boards quickly became a central component in the game industry. Everybody wants one, so every producer of game equipment needs to put one in.

An interesting bonus was that the hardware was designed to hide memory latency by parallelism. This is a smart trick that suits the thread model in the GPU shaders well.

So, graphics performance went up, but it didn't stop there. If a new GPU could make new impressive features, it would sell both games and GPUs. Thus, many important advancements started as game features.

So, it all started with that a GPU must process many pixels fast! This was the #1 task, so early GPUs could draw textured, shaded triangles much faster than the CPU.

The next generation could do matrix multiplication and divisions fast, in order to transform vertices and normalize vectors, which had then become a bottleneck on the CPUs.

The next step was programmability, programmable shaders. This was added to make Phong shading and bump mapping, new visual effects that were hard to do, or could only be done in inflexible ways.

Finally, floating-point support was added! This, too, was for visual effects, namely for light effects, using high dynamic range.

So a GPU should

- process vertices, many in parallel, applying the same transformations on each

- process pixels (fragments) in parallel, applying the same color/light/texture calculations on each

Both these tasks are suitable for parallel implementation. It is better than that, the problem is easily split into parts can be processed by one single program executed for multiple data. This makes it a SIMD friendly problem, single instruction, multiple data!

For such computations, we need less control per computation. The hardware will control many calculations instead of one.

This also gave us a different kind of threads. The whole process could have been expressed as a vector processor, explicitly grabbing chunks of data and feeding them to a vector processor. However, it was instead expressed as separate threads, processed in parallel running the same program.

This gave us the SIMT model, *single instruction, multiple threads*, which is SIMD hidden under an thread-like abstraction, but also with hardware support for this, providing each thread its identity, giving us an impression of independent threads. This model was good for graphics operations: Shader threads calculate one pixel or one vertex. CUDA/OpenCL threads may calculate anything, but typically one part of the output, and this can usually be made independent of each other.

Thus, these vital improvements all are based on needs of the game programmers, and thereby the needs of the gamers. They paid for our parallel computing platforms!

# **3.3** The arrival of GPU computing: General Purpose computation on Graphics Processing Units

The concept of GPU computing was first called GPGPU, *General Purpose computation on Graphics Processing Units*, coined by Mark Harris in 2002. The idea is to perform demanding calculations on the GPU instead of the CPU. At first, this appeared to be a wild idea, or at least a marginal possibility, but since then it has grown into a very important factor in modern computing. Results were highly varied in the early years, but the GPU advantage has grown bigger and bigger.

The concept has since then been renamed GPU computing, and more general platforms have appeared, making it easier to program and also enabling better optimizations.

### 3.3.1 Key components of the GPGPU trend

What made this possible was of course the massive parallelism of GPUs, which comes directly from the need to process large amounts of vertices and pixels,

The next key component was programmability, the introduction of shader programs, which made the GPUs much more flexible, reprogrammable for any problem.

The third vital component was the arrival of floating-point buffers. Without them, GPUs could only store and output integer information. Thereby it was vital for general purpose computing.

Initially, the support had poor precision. We could have as little as 16- or 24-bit floating point numbers, but with 32-bit floating-point we at least had decent precision, although not really impressive. High precision computations were not possible, but granted the

promising results, 64-bit floating-point support eventually arrived and has been steadily growing since then.

### 3.3.2 GPGPU/GPU computing approaches

There are several technologies for GPU computing, so let me give a brief overview. Here is a list of the most important alternatives.

- Fixed pipeline graphics

- Shader programs

- CUDA

- OpenCL

- Compute shaders

- Direct Compute

- Vulkan

The list is not exhaustive, there are many packages on top of these, and new solutions are being developed, and the current ones are revised.

### **3.3.3 Fixed pipeline GPGPU**

Even before programmable shaders, there were several results based on the old, fixed pipeline technology. Some problems could successfully be reformulated to something that could be, at least partially, computed by standard graphics operations.

Early results include Voronoi diagrams by Hoff et. al. 1999 [7], matrix multiplication by Larsen and McAllister [8] and face tracking by Ahlberg in 1999/2002 [13].

Thus, GPUs were usable for computing even back then, but the scope of algorithms was highly limited. This kind of algorithms is not of any practical interest today.

### **3.3.4 Fragment shader based GPGPU**

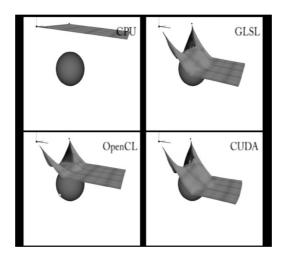

When programmable shaders arrived, the scope widened considerably. In 2005, I took part of a GPGPU project for the first time [2], and we could see an overall speedup of image processing operations of about 8 times, an amazing improvement in a business where you are happy when you can squeeze out a 10% speedup with a lot of work.

Programming is made in shader languages such as GLSL, Cg or HLSL. Initially, an assembly language was used but it was quickly phased out.

This solution has two major drawbacks. First, it requires you to re-map your data to textures, to image data, typically with four channels per pixel. This gives us a data organization that can be rather clumsy to work with. Second, the visibility of hardware features, most notably shared memory (see chapter 7), is bad compared to the following platforms. Thus, fragment shader based GPU computing is likely to be outperformed in many applications by CUDA and other later platforms.

Still, this approach should not be counted out. It is by far the most portable one. It runs on old and new GPUs. It is easy to make your algorithm run as efficiently on the latest GPUs as well as 10 year old ones. All GPUs on the market can use shaders, so there is no need for extra software, and you can run on all brands, NVidia, AMD and Intel. All you need is the standard software/drivers.

### 3.3.5 CUDA

A popular platform is CUDA from NVidia. It only works on NVidia hardware, which limits it considerably, but on the other hand, it is probably the most actively developed GPU computing platform.

It requires extra software installations, and there is a big risk that a software using CUDA has steep hardware demands due to its rapid changes. However, the active development also means that new features come here early, which often give CUDA the edge.

We often see excellent results with CUDA. For problems of highly parallel nature, 100x speedups are common, even before optimizing! Even low-end GPUs give significant boosts.

### 3.3.6 OpenCL

OpenCL is often considered the main alternative to CUDA. It works on various hardware, not only GPUs. It is developed by Khronos Group, and initially had significant support by Apple.

It is noticeably harder to get started, partially due to the wider scope of hardware, but also since the whole model is closer to OpenGL, to the extent that there are considerable similarities in how you program shaders.

### 3.3.7 OpenGL Compute shaders

An alternative that is given much less attention is OpenGL compute shaders. This is a GPU computing solution built into OpenGL. That makes it similar to OpenCL, but being part of OpenGL makes it easier to make programs with OpenGL visualization. (See chapter 15.2.) This also gives it good portability, because just like fragment shaders, it exists on all installations with a recent enough OpenGL, and all you need is the GPU drivers.

### 3.3.8 Direct Compute

DirectX also has compute shaders, a part of DirectX/Direct3D called Direct Compute. It predates the OpenGL Compute Shaders significantly. Its biggest weakness is of course that it is limited to Microsoft systems only.

### 3.3.9 Vulkan

Vulkan has sometimes been called the "new OpenGL". It is a redesign that focuses on providing good multi-thread support to graphics programming, which has become a weakness with OpenGL. It arrived officially in 2016, but now, in 2018, it is still in the process of propagating. This makes it a "Bleeding edge" technology that is not the easiest to get started with.

This could be the future main generic GPU platform for both graphics and computing. However, lack of interest from major players like Apple and Microsoft may pose problems.

# **3.4 Applications**

I claim that this is so important, but is it? Is it being used? Let me summarize some of the strongest application areas.

### 3.4.1 Image processing, image analysis and video coding

From the very first steps of GPU computing, it was clear that almost any kind of image processing fits the concept well. Among the first GPU computing results were image processing tasks, and even today, it remains one of the strongest fields. Any decent video coder must use the GPU today or it will be unreasonably slow compared to the competition.

### 3.4.2 Crypto currency mining

In the early days of bitcoins, they were often mined using GPUs. Today, that task has been taken over by ASICs, but other crypto currencies have appeared, less suited for ASIC solutions, and those currencies are mined with GPUs.

### 3.4.3 Deep learning

Deep learning basically means learning systems based on very large neural networks. Learning with neural networks has been around for a long time, and was a hot topic in the 90's, but until GPU computing arrived, it was unfeasible to handle large networks in real time.

But this is a good problem for GPUs! Simulating and updating a neural network is a highly parallel problem. And it has produced remarkable results and is now a hot trend in computer vision as well as other fields. And it was the GPUs that opened the door!

# 4. GPU architecture

So far, I have discussed why we got here and what the performance is. Now, let us look closer to how that performance is made possible.

# 4.1 SIMD and SIMT

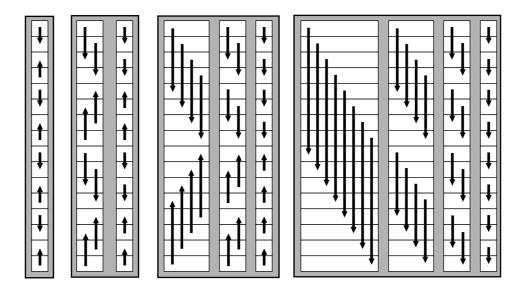

How is this possible? In the CUDA design guide, they talk about area use, that the GPU has more space assigned to computations, while CPUs waste much space on cache. This picture is no longer valid since GPUs also use a lot of space on caches these days. Instead, I would claim that the difference is that the GPU is a SIMD machine, single instruction, multiple data, while the CPU is a MIMD. These terms come from Flynn's taxonomy (Figure 2), where we also find SISD, that is old single-core systems, and the must more exotic MISD, multiple instruction, single data, where multiple processors do the same work for redundancy, for safety.

| SISD                              | MISD                                |

|-----------------------------------|-------------------------------------|

| Single instruction, single data   | Multiple instruction, single data   |

| Old single-core systems           | Multiple for redundance             |

| SIMD                              | MIMD                                |

| Single instruction, multiple data | Multiple instruction, multiple data |

| GPUs, vector processors           | Multi-core CPUs                     |

#### FIGURE 2. Flynn's taxonomy

SIMD, single instruction, multiple data, has a couple of advantages. It simplifies instruction handling, in that several cores get the same instruction. That means that the whole system for handling instructions is shared between many computations. In this sense, there is better area use.

This is, obviously, excellent for operations where one operation must be made on many data elements. So, is that so common? It is more common than you may realize, and many algorithms can be rewritten to be more SIMD-friendly.

But what about algorithms that are not SIMD-friendly, where there are differences? That can be managed by boolean operators, boolean variables used as masks. If you need two different variants, two branches, you compute both, and then trash the one that one particular line of computations does not need.

Moreover, SIMD computations are also easier to synchronize. You know exactly when the other computations (or at least part of them) are computed so some synchronizations can be skipped.

A rule of thumb here is to store data in arrays. Linked lists, pointers, tree structures, they can be hard to process in parallel, while arrays are easily passed to multiple processors.

This kind of processing situation is called (or at least closely related to) *Data Oriented Programming* (DOP). [14] While OOP tries to optimize programming for the programmer, DOP optimizes for performance, for the machine and the end user. Data structures are selected to fit the computations, instead of the programmer!

Optimizing for the end user instead for the programmer sounds like a good idea! This view is popular in the game industry, but seems virtually unknown otherwise.

# 4.2 SIMT, Single Instruction, Multiple Thread

NVidia uses the concept SIMT, Single Instruction, Multiple Thread, for their computing model. This is a variant of SIMD. I would argue that SIMT is a reformulation of SIMD, hiding the SIMD processing from the programmer, who sees the parallelism as separate threads, and gets the view of the computing as to be made in independent threads. This, however, is not the case. The threads are computed a number at a time, a *warp*.

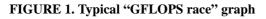

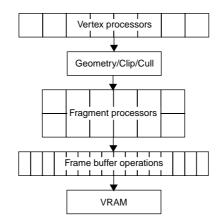

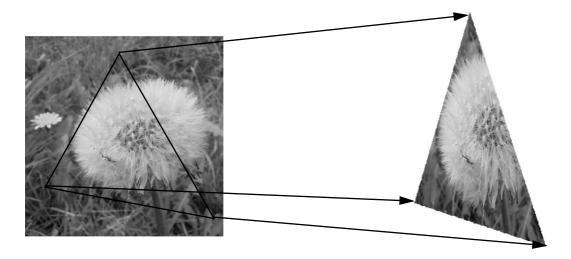

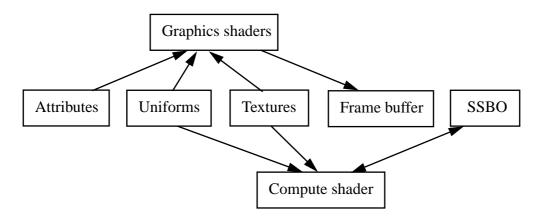

FIGURE 3. The OpenGL pipeline (simplified)

Parallelism expressed as threads is still a great improvement over handing arrays in chunks. This gives us a programming model that demands that the hardware can handle threads very fast, which is also the case for GPUs. As mentioned in chapter 3.2, this model fits a graphics processor very well.

### 4.3 The unified architecture

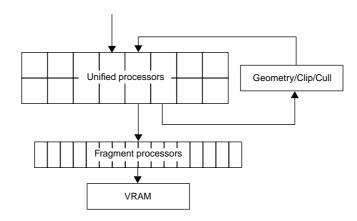

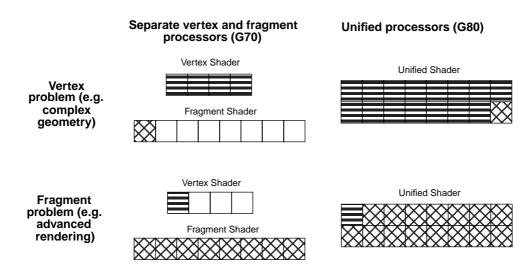

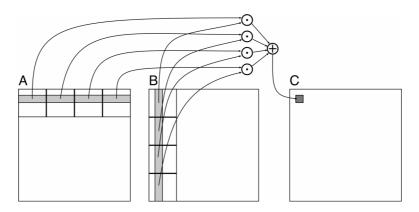

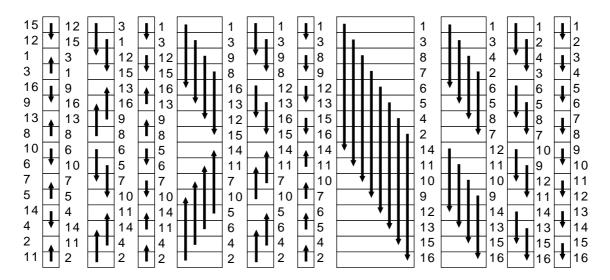

The current GPUs have a unified architecture. This is unlike early GPUs, which had a structure that closely followed the graphics pipeline, like the OpenGL pipeline, shown in Figure 3. The hardware basically had separate hardware for each step, including a number of computing cores in the vertex and fragment stages. For NVidia, this was the case up to the G70 architecture, which was roughly structured as shown in Figure 4. Note that it very closely follows Figure 3.

#### FIGURE 4. Schematic overview of the G70 GPU

In 2006, the G80 changed this, totally, All the cores in the vertex and fragment stages were collected into a pool of computing cores, all capable of performing the tasks for both stages, *unified shaders*. The data flow now passes twice through the pool of cores, as shown in Figure 5.

#### FIGURE 5. Schematic overview of the G80 GPU

This was a great success. The big advantage was that both the vertex and fragment stage could now access the whole pool, balancing the needs of the two, limiting the problem with computing bottlenecks.

For graphics, this optimized extreme situations where the balance between the difference stages is big. One such case is when there are very detailed models, with a lot of vertex computations, but little fragment processing, simple or no lighting effects etc. This is typical for 3D design situations, like CAD, where you need to see exactly how the model looks but there is no need for visual effects like Phong shading.

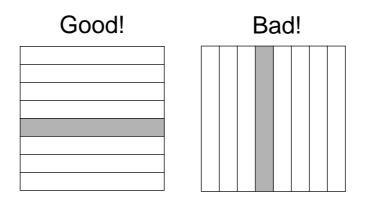

The other extreme is when you have less detailed models, but much computations at the pixel level, that is in the fragment shaders. This could be when there is a lot of visual effects, multiple light sources, bump mapping, ray marching per fragment, or even GPU computing in the fragment stage. The balancing problem is illustrated in Figure 6.

FIGURE 6. How G80 improved performance with load balancing

This new design was the first architecture that was truly suitable for GPU computing, with most of the chip dedicated to programmable computing.

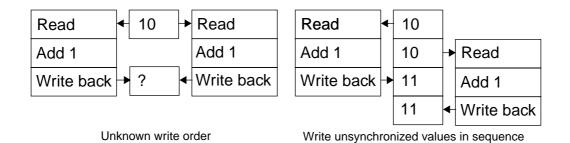

# 4.4 SMs, SPs and shared memory

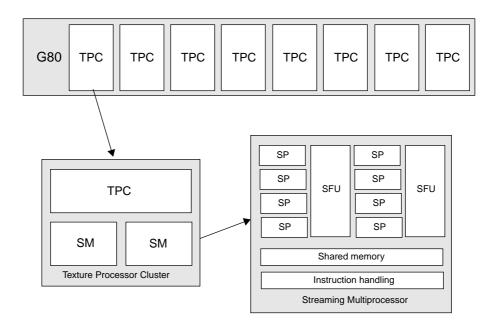

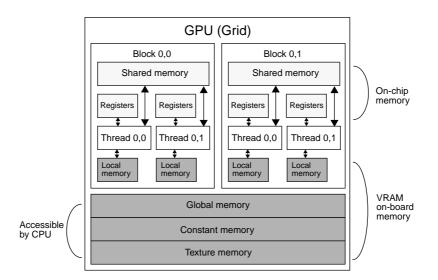

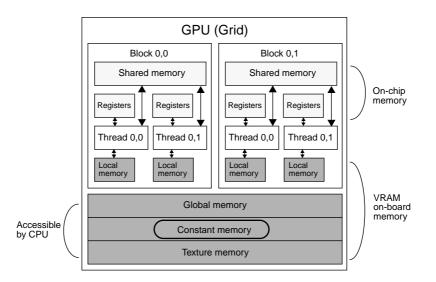

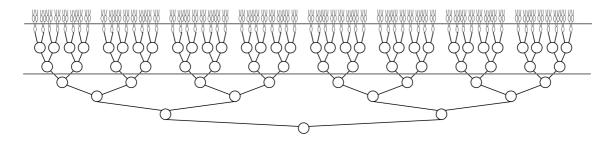

So let us have a closer look at the inside of the G80. What we find there is the design that all following GPUs are based on. See Figure 7.

We see how the processors of the G80 are grouped into eight TPCs, texture processing clusters. Each such cluster has two SMs, *streaming multiprocessors*, and hardware for texturing.

The SM concept is what we should care the most about. Inside each SM we find eight SPs, *stream processors*, which are the processing cores. However, they are not the processor cores we are used to. They are tightly coupled to a SIMD array, a vector processor, so they are essentially lanes in a single processor.

#### FIGURE 7. Vital components in the G80

We also find the SFUs, *special function units*, which corresponds to the ALU in a CPU, performing operations that we can't afford to provide separately for each SP. There is also instruction handling, register memory for each SP (not shown in the picture), and *shared memory*.

There is more inside the chip, of course. Perhaps most important to us is the thread management. Although the processing is performed as a vector processor, the computing from our point of view is made in threads, each with its own memory. These threads are managed in hardware, with automatic switching between groups of active threads. This thread switching is another key component to the efficiency. However, we don't see anything of this thread handling, we just use it and it seems totally seamless.

When doing shader programming, we see even less of the architecture. We see threads, and that is it. With CUDA, OpenCL etc., we see more. We don't care too much about the number of SMs, because the work is automatically queued over available SMs, but we do specify the split over number of threads per SM, and it is often important to make this split as optimal as possible, to distribute the work to keep the hardware busy, but also to avoid too much synchronization and passing data. We also need to plan the usage of the shared memory. More about that later.

Important note: The queuing of work over a number of SMs, which are not capable of communicating during processing other than by writing and reading global memory, and even then you can't rely on a specific block/work group being active since they are queued, is both effective, simplifying work balancing, as well as complicating many algorithms. Many seemingly simple algorithms are hard to parallelize due to the lack of communication.

So, the numbers we see in a G80 are 16 SMs and 8 cores (SPs) for each SM. These numbers are not magical in any way and change with each new architecture. The subsequent architecture from NVidia, the GT200, sports 10 SPs per SM and 30 SMs in 10 clusters, a straight upscaling.

The Fermi, in 2010, was the next major change in the hardware. Apart from even more upscaling, it surprised us by adding on-chip cache memory, the very thing that NVidia had earlier implied that was a weakness with CPUs. There was also a dramatic increase in double precision floating-point performance, 4x higher than before, implying that it was intended to strengthen the GPU computing use. Otherwise, it was business as usual with some more upscaling, 16 SMs with 32 SPs each, support for 24576 threads.

The Fermi has even had its own name, a Computing Graphics Processing Unit, CGPU. However, marketing-wise this generation was a failure for NVidia, because their strong emphasis on GPU computing let AMD take the lead, and for quite some time, AMD was the brand of choice for gamers. NVidia could not afford falling behind on their core market, so the next generation, Kepler, had more single precision support and NVidia was back on track. The following architectures, Maxwell and Pascal, has kept NVidia high on the price/performance scale again.

But don't count out AMD. While NVidia was busy taking back what they had lost in the gaming market, AMD took the lead in GPU computing with the R9 series, which for a while was the chip of choice for mining crypto currencies!

I have not said anything about the GPU architectures from AMD, but generally, they follow the lead of NVidia, in order to match the same OpenGL and DirectX generations.

# 5. Hello World!

This chapter does something completely trivial in a non-trivial way, which is even pretty unique as far as I know: We will take the super simple "Hello World" problem and solve it in parallel, not once but several times, for different GPU computing platforms. Thereby we get a first introduction to all the GPU computing platforms that I intend to cover. As you will see, the solution requires very different amounts of setup, but in the end they use kernels that are quite similar.

Let me define the problem to be solved: "Hello World!" should produce the string "Hello World!" and nothing more. For our purposes, it has to be made in parallel. This is, for all examples in this chapter, made like this: Take the string "Hello" and add, using one thread per character, the offsets 15, 10, 6, 0, -11, 1, to each character, thereby producing "World!"

This super simple problem, embarrassingly parallel and far too small for a parallel problem, thereby provides us with a first introduction to each platform. Naturally, it is a trivial problem, so we will go further with more interesting things, which is just what the original Hello World! is for. Get your first, simple program, running.

# 5.1 Hello CUDA

Most CUDA tutorials start with some simple example that is often dubbed "Hello World", although that is usually an ignorant statement since the examples usually do not output "Hello World!" as their result. This is understandable, since it is not entirely obvious how to make an example of parallel computing which has the sole purpose of producing the string "Hello world!". However, not without pride, I can present you with exactly that: A program that is short, simple, does perform parallel processing on the GPU using CUDA, and the result is indeed "Hello World!"!

So, here it is, the *real* "Hello world" for CUDA:

#include <stdio.h>

const int N = 16;

const int blocksize = 16;

\_\_global\_\_\_

```

void hello(char *a, int *b)

a[threadIdx.x] += b[threadIdx.x];

}

int main()

{

char a[N] = "Hello \langle 0 \rangle 0 \rangle 0 \rangle 0 ;

int b[N] = \{15, 10, 6, 0, -11, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0\};

char *ad;

int *bd;

const int csize = N*sizeof(char);

const int isize = N*sizeof(int);

printf("%s", a);

cudaMalloc( (void**)&ad, csize );

cudaMalloc( (void**)&bd, isize );

cudaMemcpy( ad, a, csize, cudaMemcpyHostToDevice );

cudaMemcpy( bd, b, isize, cudaMemcpyHostToDevice );

dim3 dimBlock( blocksize, 1 );

dim3 dimGrid( 1, 1 );

hello<<<dimGrid, dimBlock>>>(ad, bd);

cudaMemcpy( a, ad, csize, cudaMemcpyDeviceToHost );

cudaFree( ad );

cudaFree( bd );

printf("%s\n", a);

return EXIT_SUCCESS;

}

```

I hope the source itself explains what it is doing; it takes a string and an array of offsets to produce "World!" from "Hello ". But a few more clarifications are called for.

What you see here is, in one and the same file, both CPU and GPU code. This integration is very elegant. The amount of code to compile and launch the GPU kernel is extremely small.

The \_\_global\_\_ code is the kernel, executed on the GPU, in parallel. Note the threadIdx.x. That is the thread identifier, which must be used to calculate where in the data to operate. "Real" CUDA programs use both thread and block identifiers.

We allocate memory on the GPU from the CPU, using cudaMalloc. We can then upload and download data with cudaMemcpy, using the arguments cudaMemcpyDeviceToHost or cudaMemcpyHostToDevice to denote the copying direction. Finally, we can dispose of GPU memory using cudaFree.

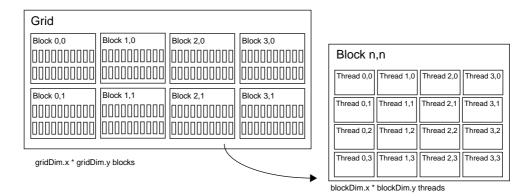

One of the most challenging issues when you start with CUDA is the concepts of grid, block and thread. The grid is the whole computing, which is split into a number of blocks, which each contains a number of threads. This division scheme describes how the computing is distributed over the GPU.

The weird statement

```

hello<<<dimGrid, dimBlock>>>(ad, bd);

```

is the actual execution of the kernel.

This version of the Hello World for CUDA works on any CUDA version. It should be noted that a simpler version exists for newer CUDA versions, using managed memory. More about that later (chapter 9.6).

### 5.2 Hello OpenCL

Hello World for OpenCL is substantially longer. However, much of the complexity is the setup.

```

#include <stdio.h>

#include <math.h>

#ifdef ___APPLE_

#include <OpenCL/opencl.h>

#else

#include <CL/cl.h>

#endif

const char *KernelSource = "\n" \

"__kernel void hello(

\n" \

\n" \

п

__global char* a,

п

__global char* b,

\n" \

__global char* c,

п

\n" \

п

const unsigned int count)

\n" \

" {

\n" \

п

\n" \

int i = get_global_id(0);

п

\n" \

if(i < count)

п

\n" \

c[i] = a[i] + b[i];

∖n"

" }

"\n";

#define DATA SIZE (16)

int main(int argc, char** argv)

ł

int err;

// error code returned from api calls

cl_device_id device_id; // compute device id

cl_context context; // compute context

cl_command_queue commands; // compute command queue

cl_program program;

// compute program

cl_kernel kernel;

// compute kernel

cl_mem input;

// device memory used for the input

array

cl_mem input2;

// device memory used for the

input array

cl_mem output;

// device memory used for the

output array

size_t global;

// global domain size for our

calculation

// local domain size for our cal-

size_t local;

culation

```

```

int i;

unsigned int count = DATA_SIZE;

// Input data

char a[DATA\_SIZE] = "Hello \0\0\0\0\0";

0};

// Output data

char c[DATA_SIZE];

// Print original data

printf("%s", a);

cl_platform_id platform;

unsigned int no_plat;

err = clGetPlatformIDs(1,&platform,&no_plat);

// Where to run

err = clGetDeviceIDs(platform, CL_DEVICE_TYPE_GPU, 1, &device_id,

NULL);

if (err != CL_SUCCESS) return -1;

context = clCreateContext(0, 1, &device_id, NULL, NULL, &err);

if (!context) return -1;

commands = clCreateCommandQueue(context, device_id, 0, &err);

if (!commands) return -1;

// What to run

program = clCreateProgramWithSource(context, 1, (const char **) &

KernelSource, NULL, &err);

if (!program) return -1;

err = clBuildProgram(program, 0, NULL, NULL, NULL, NULL);

if (err != CL SUCCESS) return -1;

kernel = clCreateKernel(program, "hello", &err);

if (!kernel || err != CL_SUCCESS) return -1;

// Create space for data and copy a and b to device (note that we

could also use clEnqueueWriteBuffer to upload)

input = clCreateBuffer(context, CL_MEM_READ_ONLY |

CL_MEM_USE_HOST_PTR, sizeof(char) * DATA_SIZE, a, NULL);

input2 = clCreateBuffer(context, CL_MEM_READ_ONLY |

CL_MEM_USE_HOST_PTR, sizeof(char) * DATA_SIZE, b, NULL);

output = clCreateBuffer(context, CL_MEM_WRITE_ONLY, sizeof(char) *

DATA_SIZE, NULL, NULL);

if (!input || !output) return -1;

// Send data

= clSetKernelArg(kernel, 0, sizeof(cl_mem), &input);

|= clSetKernelArg(kernel, 1, sizeof(cl_mem), &input2);

err

err

= clSetKernelArg(kernel, 2, sizeof(cl_mem), &output);

err

err |= clSetKernelArg(kernel, 3, sizeof(unsigned int), &count);

if (err != CL_SUCCESS) return -1;

local = DATA_SIZE;

// Run kernel!

global = DATA_SIZE; // count;

err = clEnqueueNDRangeKernel(commands, kernel, 1, NULL, &global,

&local, 0, NULL, NULL);

```

```

if (err != CL_SUCCESS) return -1;

clFinish(commands);

// Read result

err = clEnqueueReadBuffer( commands, output, CL_TRUE, 0, sizeof(char)

* count, c, 0, NULL, NULL );

if (err != CL SUCCESS) return -1;

// Print result

printf("%s\n", c);

// Clean up

clReleaseMemObject(input);

clReleaseMemObject(output);

clReleaseProgram(program);

clReleaseKernel(kernel);

clReleaseCommandQueue(commands);

clReleaseContext(context);

return 0;

}

```

In this case, the kernel is defined as a set of text strings at the top of the program. A real OpenCL program will rather put that in a separate file.

# 5.3 Hello GPGPU

In this section, we will have a look at how to write Hello World! for a fragment shader in the OpenGL pipeline. This means that the entire computation takes place by drawing bogus graphics and make computations per fragment, that is per pixel in the generated geometry.

This example exists in no less than three variants, one for old-style OpenGL, which I try to avoid, one with few dependencies, and one that uses my lab material for simplifying shader compilations and model/buffer handling (loadobj.c, GL\_utilities.c and MicroGlut).

```

// Hello World in a shader.

// Kind of twisted, since it uses signed chars.

// Modern OpenGL, using my lab material for simplicity.

#include <stdio.h>

#include <OpenGL/gl3.h>

#include "MicroGlut.h"

#include "GL_utilities.h"

#include "loadobj.h"

#include <sys/times.h>

// uses framework Cocoa

// Add offset (texUnit2) to string (texUnit)

// Negative values end up as > 0.5, adjust them!

static const char *fragSource =

"#version 150\n"

"uniform sampler2D texUnit;"

"uniform sampler2D texUnit2;"

"out vec4 outColor;"

```

```

"in vec2 texCoord;"

"void main(void)"

" { "

ш

vec4 texVal = texture(texUnit, texCoord);"

vec4 texVal2 = texture(texUnit2, texCoord);"

п

ш

if (texVal2.r > 0.5) texVal2.r -= 1.0;"

ш

if (texVal2.g > 0.5) texVal2.g -= 1.0;"

п

if (texVal2.b > 0.5) texVal2.b -= 1.0;"

...

if (texVal2.a > 0.5) texVal2.a -= 1.0;"

п

outColor = texVal + texVal2;\n"

" } "

};

// Vertex shader, pass position and texcoord

char *vs =

ł

"#version 150\n"

"in vec3 inPosition;"

"in vec2 inTexCoord;"

"out vec2 texCoord;"

"void main()"

" { "

texCoord = inTexCoord;"

п

gl_Position = vec4(inPosition, 1.0);"

"}"

};

GLfloat vertices[] = {-1.0f, -1.0f, 0.0f,

-1.0f,1.0f,0.0f,

1.0f,-1.0f,0.0f,

1.0f,1.0f,0.0f };

GLfloat texcoord[] = \{0.0f, 1.0f,

0.0f, 0.0f,

1.0f, 1.0f,

1.0f, 0.0f};

unsigned int indices[] = \{0, 1, 2, 2, 1, 3\};

Model *m;

GLuint shader;

// declare texture size, the actual data will be a vector

// of size texSize*1*4 = N

#define N 16

// test data

char a[N] = "Hello \langle 0 \rangle 0 \rangle 0 \rangle 0 \rangle 0 \rangle 0 \rangle 0

char b[N] = \{15, 10, 6, 0, -12, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0\};

unsigned char c[N];

#define texSize 4

void display()

ł

DrawModel(m, shader, "inPosition", NULL, "inTexCoord");

glutSwapBuffers();

printf("%s",a);

// and read back

glReadPixels(0, 0, texSize, 1, GL_RGBA,GL_UNSIGNED_BYTE,c);

```

```

// print out results

printf("%s\n",c);

exit(0);

}

// Not exported by GL_utilties:

GLuint compileShaders(const char *vs, const char *fs, const char *gs,

const char *tcs, const char *tes,

const char *vfn, const char *ffn, const char

*gfn, const char *tcfn, const char *tefn);

GLuint LoadTexture(unsigned char *a, GLuint texunit)

GLuint tex;

glActiveTexture(texunit);

glGenTextures (1, &tex);

glBindTexture(GL_TEXTURE_2D,tex);

glTexImage2D(GL_TEXTURE_2D,0,GL_RGBA,

texSize,1,0,GL_RGBA,GL_UNSIGNED_BYTE, a);

glTexParameteri(GL_TEXTURE_2D, GL_TEXTURE_MIN_FILTER, GL_NEAREST);

glTexParameteri(GL_TEXTURE_2D, GL_TEXTURE_MAG_FILTER, GL_NEAREST);

return tex;

}

int main(int argc, char **argv)

// set up glut to get valid GL context and

// get extension entry points

glutInit (&argc, argv);

glutInitContextVersion(3, 2);

glutInitWindowSize (4, 1);

glutCreateWindow("TEST1");

// create string texture

GLuint tex = LoadTexture(a, GL_TEXTURE0);

// create offset texture

GLuint offtex = LoadTexture(b, GL_TEXTURE1);

// Compile shader

shader = compileShaders(vs, fragSource, NULL, NULL, "vs", "fs",

NULL, NULL, NULL);

// Inform shader of texture units

glUniformli(glGetUniformLocation(shader, "texUnit1"), 0); // Texture

unit 0

glUniformli(glGetUniformLocation(shader, "texUnit2"), 1); // Texture

unit 1

m = LoadDataToModel(vertices, NULL, texcoord, NULL, indices, 4, 6);

// Ask for a redraw

glutDisplayFunc(display);

glutMainLoop();

exit(0);

}

```

Some notes: We are using all four channels of the texels, which is why the texture width is 1/4 of the data size. We also need to mess a bit with the data since we upload to unsigned chars. This problem disappears when using floating-point buffers. See chapter 11.

### 5.4 Hello Compute Shaders

OpenGL Compute Shaders is a relatively new development.

In this case, I chose to use MicroGlut for creating an OpenGL context. On the computergraphics.se page, you can also find a stand-alone Linux version complete with context creation.

Also note that this code also contains a file loader, so the kernel can be in a separate file. This is desirable for the OpenCL code as well.

Like with the fragment shader version, I have skipped some code for compiling shaders, loading a file and printing out errors.

### 5.4.1 Main program

Here is the main program code. It sets up an OpenGL context, loads and compiles a shader (by standard code, not included).

```

int main(int argc, char **argv)

// Let GLUT create a GL context

glutInit (&argc, argv);

glutInitContextVersion(4, 4); // Failed with 4.5 on my PC. The com-

pute shader works even on old-style GL!

glutCreateWindow("Hello");

// Load and compile the compute shader

GLuint p =loadShader("hello.cs");

GLuint ssbo, ssbo2; //Shader Storage Buffer Object

// Some data

#define N 16

char a[N] = "Hello \langle 0 \rangle 0 \langle 0 \rangle 0 ;

int ac[N];

int b[N] = \{15, 10, 6, 0, -11, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0\};

int *ptr;

int i;

printf("%s", a);

// PROBLEM: No bytes in shaders!

// I chose to package to int on the CPU.

// Convert string to int:

for (i = 0; i < N; i++) ac[i]=a[i];</pre>

// Create buffer, upload data

glGenBuffers(1, &ssbo);

glBindBuffer(GL_SHADER_STORAGE_BUFFER, ssbo);

glBufferData(GL_SHADER_STORAGE_BUFFER, 16 * sizeof(int), &ac,

GL_STATIC_DRAW);

// Tell it where the input goes!

```

```

// The "5" matches a "layuot" number in the shader.

// (Can we ask the shader about the number? I must try that.)

glBindBufferBase(GL_SHADER_STORAGE_BUFFER, 5, ssbo);

// Same for the other buffer, offsets, ID 6

glGenBuffers(1, &ssbo2);

glBindBuffer(GL_SHADER_STORAGE_BUFFER, ssbo2);

glBufferData(GL SHADER STORAGE BUFFER, 16 * sizeof(int), &b,

GL_STATIC_DRAW);

glBindBufferBase(GL_SHADER_STORAGE_BUFFER, 6, ssbo2);

// Get rolling!

glDispatchCompute(1, 1, 1); //Work groups launch

// Get data back!

glBindBuffer(GL_SHADER_STORAGE_BUFFER, ssbo);

ptr = (int *)glMapBuffer(GL_SHADER_STORAGE_BUFFER, GL_READ_ONLY);

// Convert int to string:

for (i=0; i < 16; i++)

a[i] = ptr[i];

printf("%s\n", a);

}

```

The main program should be of most interest, the rest is reusable code. First we create an OpenGL context. We load and compile the shader. Above, we find code that will print out error messages from the compilation. Then we create buffers on the GPU and upload the data to them, and tell the shader about the buffers.

Then we are ready to run and call glDispatchCompute(). Finally, download the result.

### 5.4.2 Kernel

As for all other cases, the kernel itself is comfortably simple.

There are a few notable peculiarities here:

You may note that the work group size is defined by the compute shader, not by the main program. However, this is not a limitation, but rather a freedom, because we can also do that from the CPU.

A more disturbing limitation is that a compute shader does not allow byte-sized variables! Therefore, the CPU part converts the data to standard-sized integers. Given that, the shader itself is as simple as the earlier ones.

```

#version 430

#extension GL_ARB_compute_shader : enable

//#extension GL_ARB_shader_storage_buffer : enable

#define width 16

#define height 1

```

// Compute shader invocations in each work group

```

layout(std430, binding = 6) buffer offsbuf {int offs[];};

layout(std430, binding = 5) buffer strbuf {int str[];};

layout(local_size_x=width, local_size_y=height) in;

//Kernel Program

void main()

{

int i = int(gl_GlobalInvocationID.x);

str[i] = str[i] + offs[i];

}

```

# 5.5 Direct Compute and Vulkan

Although we do acknowledge Direct Compute and Vulkan to be significant frameworks for our purposes, they are left out in order not to make the focus too scattered and this chapter not too repetitive. See chapter 13 for a discussion and simple example of Direct Compute.

# 6. CUDA

Our first pick for learning GPU computing is CUDA, for the simple reason that it is the easiest starting point. It sports an integrated code model that makes simple programs very simple, which is, as you saw in chapter 5, not quite the case for the others. For bigger problems, the difference rapidly gets insignificant, but for an easy start, let us use CUDA.

CUDA is officially an acronym for "Compute Unified Device Architecture" (but see the cover for my interpretation). It is developed by NVidia and is only available on NVidia boards. A G80 or better GPU architecture is required, and as you may expect, the newer hardware, the newer CUDA version you can use. It is designed to hide the graphics heritage and add control and flexibility.

Since this means that computing is taken place outside the domain of your CPU, we can consider the following model for our computing:

- 1. Upload data to GPU

- 2. Execute kernel

- 3. Download result

The same holds for other platforms, like shader-based solutions and OpenCL However, a major difference to other platforms is that CUDA has integrated source, which means that the source of host and kernel code can be in the same source file! This makes the most difference for small examples, and that is also why we start with it.

Since CPU and GPU code can reside in the same file, CUDA uses special modifiers to identify kernel code. We will soon see how that looks.

Thus, CUDA is both an architecture (essentially the G80 architecture) and a C/C++ extension. The basic model is that we spawn a large number of threads. These threads will be ran in parallel, or rather *virtually* in parallel. They will not all be computed in parallel, they will be processed in batches, as much as the GPU can handle at a time. This is exactly what happens in graphics rendering as well; fragments and vertex computations not quite executed in parallel, but in batches. The difference is that in CUDA, these batches are more visible to you. Compared to a graphics program, a CUDA program looks much more like an ordinary C program! Even though the hardware is made to process pixels, we don't see them any more, just arrays of whatever data we want to work with.

# 6.1 Simple CUDA example

Here follows a working, compileable example. This is as simple as Hello World!, but I believe that another simple example doesn't hurt, and it is even a little bit simpler since my goal was to make a truly minimal example. The central components remain the same.

```

#include <stdio.h>

const int N = 16;

const int blocksize = 16;

qlobal

void simple(float *c)

ł

c[threadIdx.x] = threadIdx.x;

}

int main()

{

int i;

float *c = new float[N];

float *cd;

const int size = N*sizeof(float);

cudaMalloc( (void**)&cd, size );

dim3 dimBlock( blocksize, 1 );

dim3 dimGrid( 1, 1 );

simple<<<dimGrid, dimBlock>>>(cd);

cudaMemcpy( c, cd, size, cudaMemcpyDeviceToHost );

cudaFree( cd );

for (i = 0; i < N; i++)

printf("%f ", c[i]);

printf("\n");

delete[] c;

printf("done\n");

return EXIT SUCCESS;

}

```

In the code, you can easily spot the computing kernel, a thread identifier, allocation of GPU memory, specification of 1 block and 16 threads, the kernel call, the readback of data to CPU, and deallocations.

# 6.2 Modifiers for code

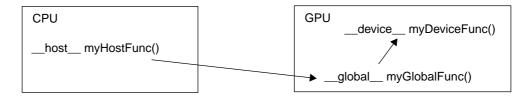

Since we are mixing CPU and GPU code, we must instruct the compiler on what is what. Three modifiers are built into CUDA to specify how code should be used:

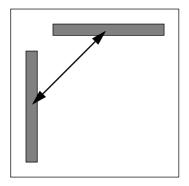

\_\_global\_\_ executes on the GPU, invoked from the CPU. This is the entry point of the kernel. \_\_\_device\_\_\_ is local to the GPU, not callable from the CPU. You use this for subroutines and methods used by the main kernel, the \_\_\_global\_\_\_.

<u>host</u> is CPU code. This is superfluous, since it is the default. You may use it for making your code more readable.

The modifiers are illustrated in Figure 8.

FIGURE 8. CUDA code modifiers

# 6.3 Memory management

The memory management calls are similar to the calls in the C libraries, where we have malloc(), calloc() and free(), but now they are calls done by the CPU to allocate and manage memory on the GPU.

cudaMalloc(ptr, datasize)

This allocates a chunk of memory on the GPU.

cudaFree(ptr)

This frees the memory allocated by cudaMalloc.

```

cudaMemCpy(dest, src, datasize, arg)

```

This copies data between CPU and GPU, datasize bytes from src to dest. This is rather peculiar, you must specify direction using these constants:

```

arg = cudaMemcpyDeviceToHost

or cudaMemcpyHostToDevice

```

These constants may seem unnecessary, but the dest and src pointers can not be identified as CPU or GPU memory so we need to keep track of that ourselves.

The easiest way to manage memory with CUDA, if you are on a fairly recent GPU (CUDA capability 6) is to take advantage of *unified memory*. This allows you to access the same memory from CPU and GPU. You must still allocate it with CUDA calls.

```

cudaMallocManaged(ptr, datasize)

```

For this kind of memory, no cudaMemCpy is needed, just pass the pointer.

To make matters even easier, you can declare a variable <u>managed</u>, which will then have the same capability. We will discuss this further in chapter 9.6.

# 6.4 Kernel execution

The kernel is executed by a call with very odd syntax:

```

simple<<<griddim, blockdim>>>(...)

```

That is KERNELNAME<<<a href="https://www.argument1">kERNELNAME<<<a href="https://www.argument2">kernet2</a>>>(some other arguments)

The arguments in the parenthesis are the argument sent to the kernel entry point, the \_\_\_\_\_global\_\_\_. The ones within <<<>>> are something else, they specify the size of the computation, and how it should be split into blocks and threads.

The *griddim* argument specifies the number of blocks, and the *blockdim* argument specifies number of threads per block.

When working with blocks and threads in the kernel, you need to use the built-in variables *threadIdx*, *blockIdx*, *blockDim* and *gridDim*, which tells the thread what thread numer it has, in what block, and the dimensions of each (as specified above).

If you are used to OpenGL, you may note that no prefix is used for built-in variables, like GLSL does. We will look further into blocks and threads in chapter 6.7.

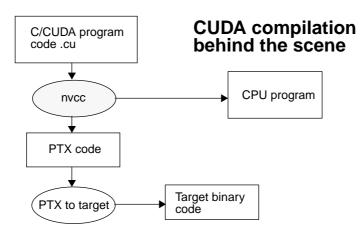

# 6.5 Compiling Cuda

If you start from the CUDA development kit, you will find that the CUDA examples are compiled by gigantic makefiles. Don't panic, they are just auto-generated makefiles with a lot of unnecessary fluff. It all boils down to calling a single compiler, *nvcc*.

nvcc is nvidia's CUDA compiler. On Unix systems you will usually find it in

/usr/local/cuda/bin/nvcc

#### FIGURE 9. CUDA compilation

Source files are suffixed .cu. In order to compile a simple example like "simple" above, all you need to do is a simple command-line like this:

nvcc simple.cu -o simple

Of course it is not quite that simple for all cases. Like with all compilers, there are options for including libraries as well as other options, enabling/disabling language features etc.)

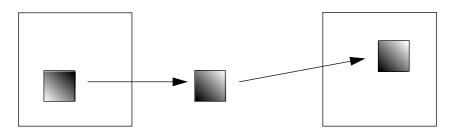

However, this simplicity hides a much more complex compilation than we are used to. What happens behind the scene is illustrated in Figure 9.

The nvcc compiler doesn't just compile a program, it splits the code into CPU and GPU parts, sends the CPU part to GCC/G++, and compiles the other to something called PTX code. This code is an intermediate code, which is compiled to your target GPU when executed. This two-step process is there to allow a compilation for any kind of (supported) GPU, while still allowing each GPU to have the instruction set it needs.

## 6.5.1 Compiling CUDA for larger applications

It may seem like your CUDA-using application should be written entirely as .cu files. Anyone involved in a large project that needs CUDA acceleration late in the process will realize that that is out of the question. Fortunately, this is not the situation, we do not need to port the rest of the project.

For instance, if your program is a C or C++ program, you can compile it with gcc as usual, and then link with the CUDA parts. You use nvcc for the .cu files and gcc for .c/.cpp files. You can mix in any language that produces code that can be linked with C/C++. You may do the final linking with gcc or g++. In any event, the final linking must include C++ runtime libs.

This gives us one little hint: .cu files are really C++. Indeed, .cu allows us to use C++ classes, even in the kernel!

#### 6.5.2 Example of multi-unit compilation

Thus, multi-unit compilation is quite easy. Here follows a simple example with one .c file and one .cu file. They are called cudademokernel.cu and cudademo.c.

I compile them with